2025年,AI高速運算的競賽持續升溫。全球AI供應鏈都面臨相同挑戰:電子頻寬已逼近物理極限,光電整合已成為趨勢。在這波升級浪潮中,矽光子技術(Silicon Photonics)與CPO(Co-Packaged Optics)封裝成為關鍵技術。

從NVIDIA宣布導入矽光子技術、Broadcom加速乙太網路新品布局,到台積電推進緊湊通用光子引擎(Compact Universal Photonic Engine, COUPE),產業領導者積極投入。台灣政府也將矽光子列入「AI新十大建設」之一,預計在2028年完成矽光子供應鏈自主。經濟部更投入29億元光電前瞻技術計畫,目標將高雄打造為未來的矽光子核心基地。

即使具備全球頂尖的研發團隊與政府資源挹注,矽光子走向量產仍面臨多重挑戰。當光子電路(Photonic Integrated Circuit, PIC)整合進半導體晶片,整套驗證流程會從電路(Electrical Integrated Circuit, EIC)問題延伸至光子問題。研發團隊即使突破架構設計,仍可能因量測速度太慢、光損位置難以精準定位、封裝後出現不可逆故障、良率難提升等因素受阻。

本文將拆解矽光子量產的核心挑戰,並介紹如何協助工程師加速CPO研發,邁向量產化。

矽光子:CPO核心技術解析

矽光子元件包含波導(Waveguide)、調變器(Modulator)、分波器(Demultiplexer/Mux)、耦合器(Coupler)以及光電二極體(Photodiode, PD),均可利用互補式金屬氧化物半導體(Complementary Metal-Oxide-Semiconductor, CMOS)製程製造。

這意味著光子元件可沿用既有晶圓產線大規模生產,並具備與EIC同封裝或同晶圓整合的能力。當PIC與EIC整合於同一平台,即可突破電子互連的物理極限,實現寬頻、低功耗、高速傳輸、高抗干擾能力,並有效減少電子互連中常見的趨膚效應(Skin Effect)、串音(Crosstalk)與插入損耗(Insertion Loss, IL)急劇上升等問題,使序列化/解序列化(Serializer/Deserializer, SerDes)互連能耗從15–25pJ/bit降至1–3pJ/bit,同時減輕熱管理負擔。

矽光子量產前的三大驗證挑戰

雖然矽光子具備高速與低功耗優勢,但對於習慣處理電子電路的工程師來說,PIC代表的是全新的物理現象與測試方法。目前產業在推動矽光子量產時,驗證階段普遍面臨三大關鍵挑戰:

元件測試速度瓶頸

目前矽光子元件測試速度與電子測試相比仍顯緩慢,無法跟上高速介面與AI晶片開發節奏。量測IL、偏振依賴損耗(Polarization Dependent Loss, PDL)、光響應度(Responsivity)與頻譜響應(Spectral Response, SR)時需逐波長掃描取樣。與電子電路可快速用探針測試不同,光子元件在光纖耦合、波導測試或調變器量測時,每次測試都要重新調整入光角度與焦距,導致量測效率低下。

光損難以精準量測

業界的矽光子光學晶圓驗收測試(Optical Wafer Acceptance Test, OWAT)多依賴光反射量測與頻譜分析,推斷可能漏光位置。但這種方法僅能提供估算,無法精準掌握光損來源。多數晶圓廠僅檢查總體IL,工程師能觀察光效能下降,但難以判斷光損數值與來源。缺乏精確位置與量化數值會導致設計、封裝與量產反覆受阻,難以有效收斂。由於PIC對干擾較為敏感,且造成光損的因素分散且複雜,使光損不僅難以預測,更難以靠傳統光學量測方法進行來源定位。

由於矽光子技術多應用於高速介面與AI運算相關驅動與控制電路,其搭配的EIC往往採用5nm、3nm等先進製程,單顆晶片成本相對高昂。相較之下,PIC多以成熟製程生產,成本較低。若等到異質整合階段(如PIC與EIC貼合,組成CPO模組)才發現PIC光損問題,將連帶造成整顆EIC無法回收,整組模組也可能報廢,造成損失放大。因此,PIC必須在晶圓階段就進行晶圓階段篩選。

因為風險極高,PIC晶片常需全檢(100%檢查),以避免在PIC與EIC貼合後才發現問題。然而,全檢不僅耗時、成本高,也無法從根本上改善矽光子量產階段的設計迭代效率。這些量測限制,正是矽光子從技術突破邁向大規模量產時的主要瓶頸之一。

封裝熱源風險

矽光子元件高度整合、光與電距離極近,模組內部往往潛藏局部熱源。這些微量熱源不可見,也無法透過傳統電測偵測。工程師通常只能從IL、PD Responsivity或位元錯誤率(Bit Error Rate, BER)等電光參數變化觀察問題,但無法直接判斷熱源位置與強度。若未在晶圓或晶片階段提前檢測,即時監測與定位,封裝與運作後可能引發波導漂移、光損增加、熱光效應失衡、甚至元件提早老化,整顆模組可能報廢,降低良率。

宜特×光焱科技:矽光子驗證全流程解方

精準光損量測

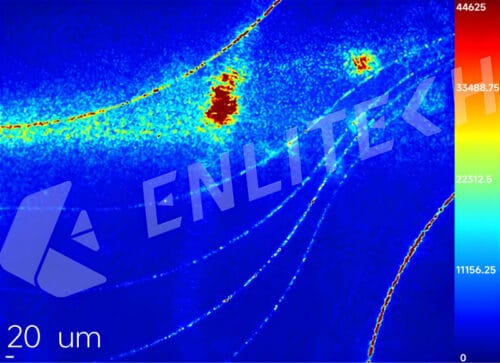

宜特與光焱科技(Enlitech)合作,整合雙方專長,打造光電整合量測平台。可針對晶圓、晶片與模組進行高速光損(Insertion Loss, IL)Mapping。Night Jar矽光子測試解決方案(Silicon Photonics Testing Solution)能精確指出異常die及結構,顯示漏光位置與光損精確數值,提供可視化光損分布與局部定位(圖1、圖2)。

速度與精度提升

Night Jar量測速度快,每秒即可完成一個區域影像拍攝,整體效率比市面上快一倍。內建高精度耦光對位模組(Alignment Module)精準度可達0.2nm,提升量測穩定性與重複性,使光損資料更可靠(圖3)。

光損與熱源監測

結合光熱影像(Optical-Thermal Imaging)分析,可揭露模組潛藏熱源(Hotspots),協助工程師在封裝前掌握熱漂移、局部過熱、調變器或雷射源熱累積、PD受熱導致性能變動等情況,為封裝前的風險管理提供依據。

光損定位與結構分析

精確定位光損後,可聚焦特定元件與區域,進行物性分析(Physical Failure Analysis, PFA)與材料/結構分析(Material Analysis, MA),透過SEM、Dual-Beam FIB、Plasma FIB、TEM、X-ray、SIMS等手法揭露波導、耦合器、調變器等元件內部微缺陷,加速設計收斂與製程最佳化。

CPO可靠度測試

組裝完成的CPO光電模組(如COUPE)可進行全項可靠度測試流程,包括溫度循環(Temperature Cycling Test, TCT)、濕熱測試(Highly Accelerated Stress Test, HAST)、振動、落塵等。所有測試以IL變化量作為判斷標準。資料化與統計化量測可有效量化風險,支援工程師做出精準設計與製程決策。

從基板(Substrate)與測試座(Socket)設計、光/電測試、可靠度驗證、故障分析與結構分析,到封裝挑戰的解決,流程越順,矽光子技術邁向量產的速度就越快。掌握完整驗證手法,能加速COP光電整合研發,推動光速時代光速到來。

(本文由宜特科技提供)